随着系统复杂度的不断提高,传统封装技术已不能满足多芯片、多器件的高性能互联。而三维系统级封装(3D-system in package, 3D-SiP)通过多层堆叠和立体互联实现了芯片和器件的高性能集成。其中,硅通孔(Through silicon via, TSV)结构在3D-SiP 中发挥着极为关键的作用。系统性的回顾了 TSV 技术的研究进展,包括TSV 的技术背景、生产制造、键合工艺和应用特色,同时对比并总结了不同制造工艺和键合工艺的优缺点,如制造工艺中的刻蚀、激光钻孔、沉积薄膜和金属填充,键合工艺中的焊锡凸点制备、铜柱凸点制备和混合键合,讨论了 TSV 当前面临的挑战,展望了 TSV 未来的发展趋势。

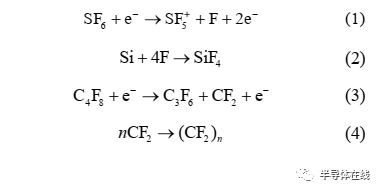

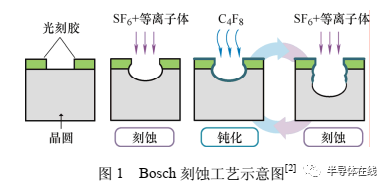

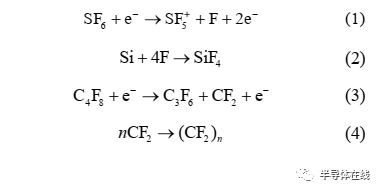

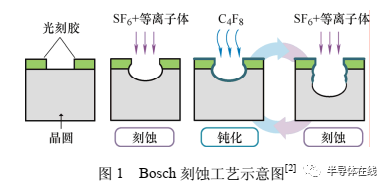

由于半导体特征尺寸逼近物理极限,芯片的设计难度和制造成本明显提升。通过微缩特征尺寸以实现芯片性能翻倍难以继续,但系统对性能提升的要求没有降低,系统复杂度仍在持续增长。为了满足需求,研究人员从封装层面上构建系统级封装(System in package, SiP)。与传统封装技术相比, SiP更能满足集成电路向更高集成度、更高性能、更高工作频率发展的要求。三维系统级封装(3D-SiP)技术是先进封装技术的发展方向之一,通过多层堆叠和立体互联,能够大幅提高组装密度和封装效率。在 3D-SiP 中, 垂直互连结构对三维集成封装以及实现系统整合具有不可替代的作用,其中硅通孔(Through silicon via, TSV)互连结构在先进封装领域中是最为普遍的结构。TSV 技术是指在硅介质层上开孔并填充导体?以实现介质层上下方垂直互联的技术。TSV 结合微凸点,能够在三维方向上获得最大的堆叠密度及最小的外形尺寸,显著提升了系统性能,降低了系统功耗,因此被视作是继引线键合和倒装芯片之后的第三代封装互连技术。本文重点介绍 3D-SiP 中垂直互联结构的关键技术:硅通孔技术, 对 TSV 的制造工艺、 键合工艺、技术应用、优势与挑战等进行阐述、归纳和总结,并对 TSV 的未来发展趋势做出预测。TSV 技术是一种高密度封装技术,通过硅通孔的垂直电气互连以实现更小的互连长度、降低信号延迟以及减小电容和电感。而在 TSV 制造工艺中,通孔、 侧壁涂层以及导体填充等环节对 TSV 的实际性能表现起着关键作用。Bosch 刻 蚀是 一 种 典 型 的 深 反 应 离 子 刻 蚀(Deep reactive ion etching, DRIE)工艺,分为刻蚀和钝化两个循环周期。图 1 展示了 Bosch 刻蚀工艺的过程。在刻蚀周期,通过 SF6 与 Si 的短暂接触完成一次较浅的纵向刻蚀。SF6 在射频源的作用下电离为等离子体,等离子体中的高活性 F 原子与 Si发生反应生成可挥发的 SiF4,其反应过程如式(1)和式(2)所示。在钝化周期, C4F8 在等离子体中形成氟化碳类高分子聚合物,沉积在 Si 表面上以形成一层钝化膜,能阻止 Si 与 SF6 继续反应,其反应过程如式(3)和式(4)所示。在下一个刻蚀周期,离子在偏压源的作用下从垂直方向上溅射轰击钝化膜,使底层的 Si 表面暴露,而侧面的钝化膜未被破坏。如此循环若干次后?可形成具有一定深度的通孔,同时避免了横向刻蚀。

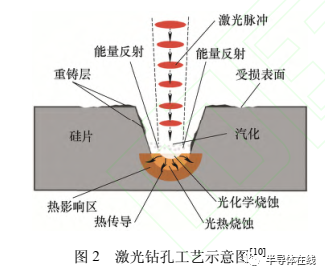

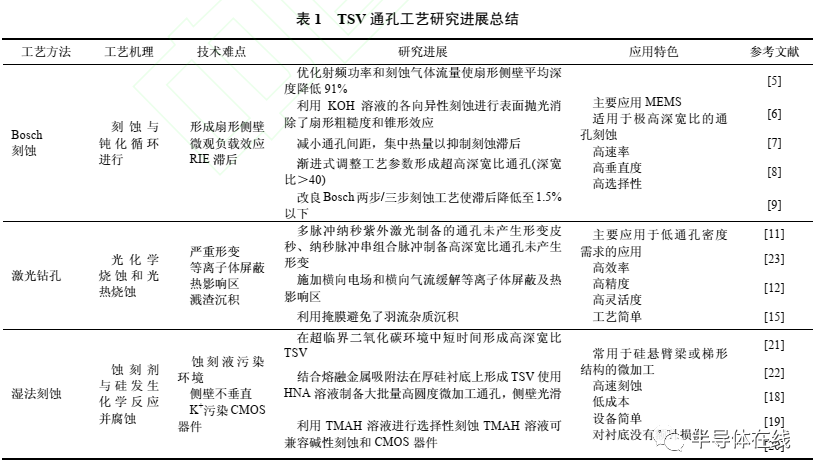

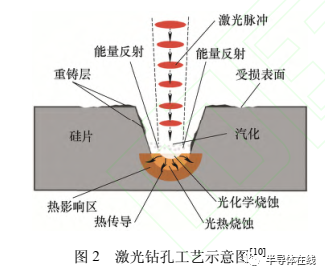

由于 Bosch 工艺中的刻蚀过程为各向同性刻蚀,在刻蚀和钝化交替进行若干次后,最终会形成扇形的通孔侧壁。扇形侧壁会导致 TSV 的绝缘层和阻隔层产生应力和电场的集中,引发铜扩散和泄漏等问题。另一方面, Bosch 工艺的基础性限制是微观负载效应。对于相同孔径的通孔,通孔密集区域对刻蚀离子的消耗量大,造成供给失衡,刻蚀速率下降,最终导致在同一基板或晶圆上不同密度区域的通孔刻蚀深度不同。另外,对于不同孔径的通孔,反应离子刻蚀(Reactive ion etching, RIE)会产生滞后。由流体动力学可知,气体传输在纵横比大于1 的结构中会被限制,随着刻蚀深度的增加,通孔的深宽比逐渐增大,而刻蚀速率会逐渐减小,直至刻蚀停止,宽孔径通孔刻蚀深,细孔径通孔刻蚀浅。针对上述技术难点, PARK 等在 DRIE 之后用SF6 等离子体进行干法刻蚀,通过优化射频功率和刻蚀气体流量,将扇形侧壁的平均深度降低 91%。扇形侧壁的凸起处与 SFx 离子和 F 自由基接触的概率大于凹陷处,故凸起处的刻蚀速率高于凹陷处,进而形成平滑的侧壁。FRASCA 等增加“米开朗基罗”步骤用于侧壁抛光。KOH 在(110)平面刻蚀的最快,在(111)平面刻蚀的最慢,通过 KOH 溶液在晶体取向为(110)的硅晶圆上的各向异性刻蚀去除侧壁的扇形部分,形成了相对平整的侧壁。总之,侧壁越趋于平滑,其稳定性和可靠性越高。对于微观负载效应, WANG 等在标准 Bosch 工艺的每 5个循环周期后插入一个冷却步骤,利用密集区域的热量集中以提高刻蚀速率,增加刻蚀深度,弥补微观负载效应。对于 RIE 滞后现象, TANG 等发明了一种渐进式调整工艺参数的 Bosch 工艺。但是该工艺需要精密且昂贵的机器,并且增加了过程复杂性。为了降低复杂度, GERLT 等通过延长钝化时间, 在刻蚀深度为 50 μm 时将刻蚀滞后降低到 1.5%以下。由于细孔径通孔中的聚合物沉积速度比宽孔径慢, 所以在固定的沉积时间内形成的钝化层更薄,而之后的各向异性离子轰击与深宽比无关,所以细孔径通孔中的 Si 将比宽孔径更快地暴露。尽管最后的 SF6 刻蚀在细孔径通孔中较慢,但是由于底部的Si 暴露得更早,所以其刻蚀早于宽孔径通孔,提高了刻蚀效率。因此,通过延长钝化时间可以显著降低 RIE 滞后。Bosch 刻蚀工艺主要应用于 MEMS,适用于极高深宽比的通孔刻蚀,通孔侧壁接近垂直,在硅基板上的刻蚀深度可达数百微米。自 Bosch 工艺发明以来,该工艺根据即将到来的新应用进行不断调整和改进。其关键的工艺特征是高掩膜选择性、高刻蚀速率、良好的刻蚀速率均匀性和轮廓精度、缺口抑制能力以及高深宽比刻蚀能力。在目前的生产条件下,对于 25%的开口面积,硅刻蚀速率接近20 μm/min,对于接近 50%的超大开口面积,硅刻蚀速率也能达到为 9 μm/min,均匀性不低于±5%。激光钻孔是一种干法刻蚀工艺,利用高能定向激光束与硅衬底之间的烧蚀效应来制备通孔,高效且环保。图 2 展示了激光钻孔工艺的过程。光化学烧蚀和光热烧蚀是激光钻孔的主要机理,硅材料的刻蚀过程可以视作这两个过程的组合。光化学烧蚀是非热过程,材料吸收激光脉冲光子后致使原子键断裂,进而引起材料分离。在光热烧蚀中,激发能和电离能从电子快速耗散到晶格,材料表面迅速升温并发生爆发式熔化和汽化。

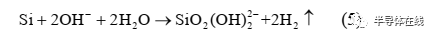

对于激光钻孔,理想通孔具备高圆度和低锥度的特征,没有热影响区和重铸层,而实际制造出的通孔往往产生较严重的形变。通孔的形变是由机械劈裂而非激光钻孔造成的,在孔的底部,孔径变宽并形成桶形横截面,对于孔径较大、在多脉冲和高能量脉冲下产生的通孔,展宽效应更为明显。另外,等离子体屏蔽也是利用强、短脉冲实现高速精密烧蚀时存在的关键问题之一。在基板表面,由于受激光热影响区和烧蚀精度的影响,通孔周围的材料可能会因高温而被破坏,致使钻孔的效率和通孔密度较低。同时,在激光钻孔的过程中会产生溅渣,随后凝固并附着在孔的周围,大大降低了钻孔的质量和表面平整度。在通孔腔内,硅熔化后会快速凝固,易在通孔内壁上形成球形瘤, 致使内壁粗糙度较大,难以沉积连续的绝缘层和种子层,并且内壁亚表面的热损伤较大,影响后续通孔填充的可靠性。对于等离子体屏蔽以及形变问题,关键在于加快等离子体及蒸汽的流动。TAN 等提出一种多脉冲纳秒紫外激光的钻孔方法。首次脉冲串烧蚀产生的空间为等离子体和蒸汽提供了通道和膨胀空间,因此降低了等离子体密度和温度,有效避免了等离子体屏蔽,之后的烧蚀将继续移除材料并且避免形变的产生。与之类似,可以通过在孔口处施加横向电场和横向气流来辅助激光钻孔。等离子体中的带电粒子在电场的作用下发生移动,横向气流加快了混合羽流的流动和扩散,降低了孔口处混合羽流的密度,有效缓解了等离子体屏蔽。此外,横向气流增强了基板表面的空气流动以增强冷却效果,减小了热影响区。虽然纳秒紫外激光的钻孔效率较高,但热损伤会降低钻孔精度。与纳秒激光钻孔相比,皮秒、飞秒激光钻孔具有更短的脉冲宽度和更高的钻孔精度,造成的热损伤更小,却牺牲了钻孔效率。对于溅渣沉积问题, HO 等尝试用掩膜减少钻孔表面的羽流杂质。熔融颗粒溅射到孔外后沉积在孔口周围的掩膜上,分离掩膜时将部分溅渣去除,有效地降低了溅渣沉积高度,提高了表面平整度。激光钻孔是一种方式灵活的无接触加工方法,具有高精度、高效率、高深宽比等优点。激光束直接作用于材料,不存在机械磨损,同时避免了材料污染。由于激光具有较高的能量密度,因此钻孔效率很高,且基板的热变形和机械变形都很小,有效地提升了钻孔质量。由于绝大部分激光钻孔方法不需要掩膜,因此具有更高的灵活度。由于受激光热影响区的影响,激光钻孔的通孔密度较低。但对于低密度通孔需求的应用(如 MEMS),激光钻孔具有低成本的优势。另外,通过使用短脉冲的皮秒和飞秒激光,有利于在基板上制造出精细的结构。在其他湿法刻蚀技术出现之前, KOH 刻蚀是一种主流的湿法刻蚀方法。KOH 刻蚀的机理是通过KOH 溶液与衬底发生反应, 去除未被掩膜保护的材料部分。在刻蚀过程中只有硅被去除,衬底上的其他材料不会被破坏,该过程主要受温度、搅拌速度和溶液浓度的影响,其反应过程如式(5)所示。

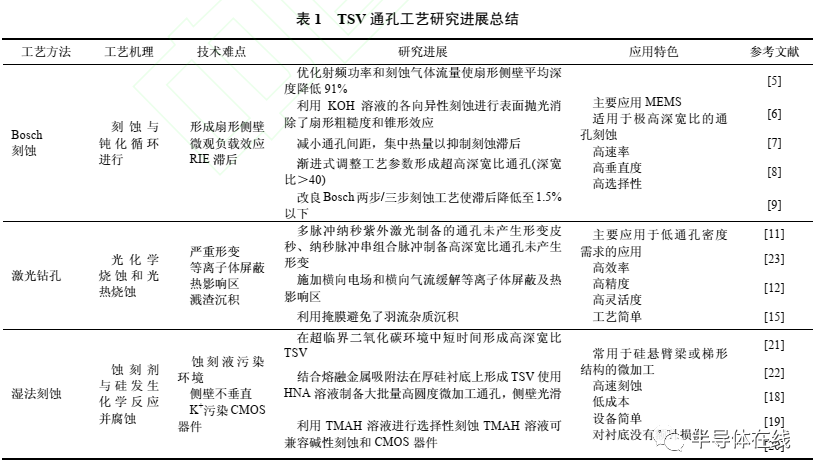

KOH 刻蚀对温度敏感。温度能够影响刻蚀过程中局部反应速率, 进而影响整个刻蚀过程的同步性。同时, 局部反应释放的热量也会加速局部刻蚀过程,增加了整体刻蚀的不均匀性。由式(5)可知,在反应过程中会产生氢气,氢气可能会形成微掩膜,阻止反应持续进行。此外,由于蚀刻剂的流动会影响硅片的表面形态,因此湿法刻蚀难以精确控制刻蚀深度。通过 KOH 刻蚀形成的通孔侧壁不是垂直的,侧壁形状取决于晶圆的晶体取向,因此不适用于制备垂直的高深宽比 TSV。避免蚀刻剂造成污染也是湿法刻蚀的技术难点之一, KOH 溶液中的 K+可能会污染晶圆上的 CMOS 器件,废弃的蚀刻剂也可能会造成环境污染。为了制备具有垂直侧壁的高深宽比通孔,研究人员在湿法刻蚀的试剂上做了许多尝试,如 GUAN等公布了一种用于制造高圆度微通孔的高选择性 氢 氟 酸 - 硝 酸 - 醋 酸 (Hydrofluoric acid-Nitricacid-acetic acid, HNA)刻蚀体系。硝酸的强氧化性能够将硅氧化为 SiO2, 氢氟酸与 SiO2 生成络合物并溶解,由于 HNA 溶液为各向同性刻蚀,因此通过使用 HNA 溶液能刻蚀出高圆度光滑通孔。但是,由于 HNA 溶液与 Si 的反应为自催化放热反应,亚硝酸的积累和溶液温度的升高可能会导致反应失控。对 此 , CHENG 等研 究 用 四 甲 基 氢 氧 化 铵(Tetramethyl ammonium hydroxide, TMAH)溶液完成选择性湿法刻蚀,有效避免了反应失控。对于蚀刻液可能引起的污染问题, BAGOLINI 等通过TMAH 溶液实现碱性刻蚀与 CMOS 器件的兼容, 不需要额外的工艺步骤。与碱金属氢氧化物相比,氨基氢氧化物在反应后不会在器件表面残留金属离子,从而避免器件污染。在工艺方面,通过将电流和紫外线引入到湿法刻蚀工艺中实现高速刻蚀,即光 辅 助 电 化 学 刻 蚀 (Photo-assisted electrochemical etching,PAECE)。在刻蚀过程中,由于电化学的氧化作用,局部材料被溶解,而紫外光会加速硅表面的氧化反应,显著提高刻蚀效率。KOH 刻蚀是一种高效、 有前景和低成本的晶圆刻蚀技术。在 MEMS 制造中, KOH 刻蚀通常用于硅悬臂梁或梯形结构的微加工,但它并不是制造高深宽比 TSV 的最佳方法。在其他刻蚀方法出现之前, KOH 湿法刻蚀是制造微通孔的唯一手段,并且具备很多优点,如该方法不需要复杂的设备,使低成本的大规模生产成为可能;使用的化学溶液对基板没有额外的损伤等。PAECE 主要用于制造高深宽比的通孔, 如 MEMS 中的电容结构和三维封装中的TSV。研究人员将 PAECE 分别与超临界二氧化碳技术和熔融金属吸附法结合使用,都成功制备出高深宽比、无缺陷的 TSV。表 1 总结了 TSV 通孔工艺的相关研究进展。目前主要的通孔工艺有 Bosch 刻蚀、激光钻孔和湿法刻蚀。传统 Bosch 刻蚀工艺具有侧壁粗糙、离子刻蚀滞后等缺陷,而通过优化工艺参数和碱性溶液抛光可降低扇形粗糙度,通过缩小通孔间距、调整工艺参数可缓解刻蚀滞后。传统激光钻孔工艺具有形变严重、溅渣沉积等缺陷,而通过多脉冲、横向电场及气流辅助可有效改善通孔形变,通过制备掩膜可避免溅渣沉积。湿法刻蚀中, KOH 刻蚀具有设备简单、低成本的优点,在早期是最主要的通孔刻蚀方式,随后研究人员通过研发新的碱性溶液弥补了其侧壁不垂直、污染 CMOS 器件等缺陷;PAECE是一种高效率、低成本的刻蚀工艺,配合先进的填充工艺可以制备高质量 TSV,但废弃的蚀刻液可能会造成环境污染。

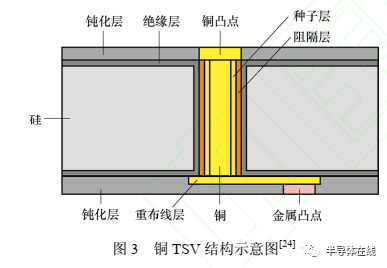

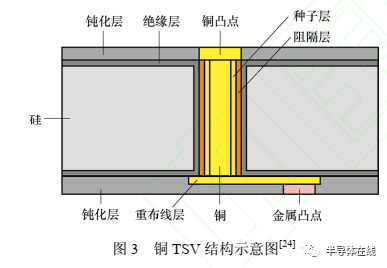

TSV 的内部侧壁结构主要由三部分组成,包含绝缘层、阻隔层和种子层,如图 3 所示。绝缘层的完整性和厚度的均匀性会影响到器件电性能的可靠性、热机械应力的集中和裂纹的产生,阻挡层的完整性决定了金属离子的扩散,种子层的完整性直接影响到通孔的填充机制——电流密度的分布、添加剂的吸附、金属离子的吸附和沉积等。因此,侧壁涂层工艺的质量直接影响到 TSV的形成和性能。

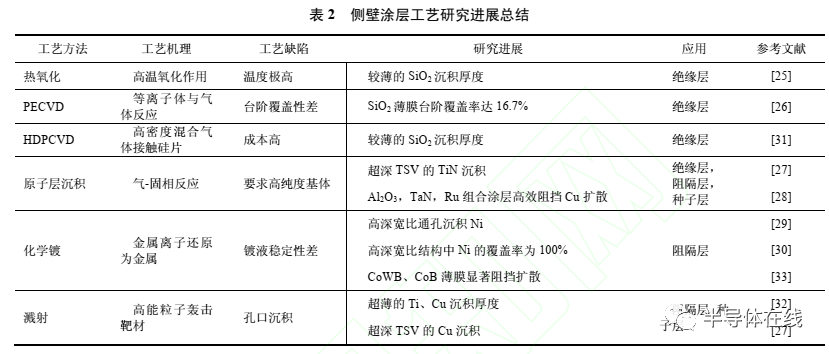

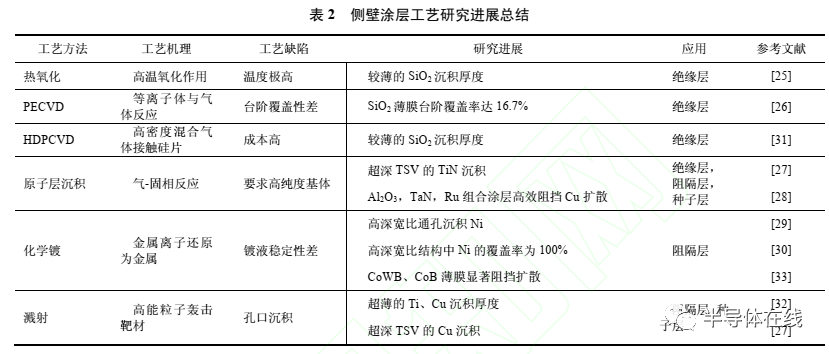

沉积绝缘层是 TSV 工艺中特殊的一步。由于Si 是半导体材料,与导体接触会导致漏电,而绝缘层可以避免 TSV 之间发生泄漏和串扰。SiO2 是常用的电介质材料,具有低漏电和低损耗的特点,并且在热膨胀上与 Si 匹配。SiO2 绝缘层可以用热氧化法或 等 离 子 增 强 化 学 气 相 沉 积 (Plasma enhancedehemical vapor deposition, PECVD)等工艺制备,同时还要考虑基板的材质是否耐高温而选择具体的工艺。例如, LIN 等用热氧化法在通孔中形成了厚度为 1 μm 的 SiO2 绝缘层。其工艺流程是在高温条件下使硅片表面发生氧化反应形成 SiO2 薄膜,该方法工艺简单,制备得到的薄膜性能优越,但热氧化工艺需要上千度的高温, 一般材质的基板无法承受。由于 PECVD 技术引入了高能量的带电粒子参与化学反应,降低了沉积过程对温度的要求,因此使薄膜可以沉积在一些熔点不高的材料上,但难以完成高深宽比通孔的台阶覆盖。对此,刘晓阳等通过优化 PECVD 工艺参数,使用正硅酸乙酯液体反应源,实现了深宽比为 6:1 的 TSV 约为 16.7%的绝缘层台阶覆盖率。在 PECVD 工艺中,通过适当降低低频功率和腔室压力,调整分步沉积次数能够提高台阶覆盖率。阻隔层可以防止导电填充物扩散到绝缘层和衬底中,并且提高导电填充物与衬底的粘合度。阻隔层材料包括 Ti、 TiN、 TiW、 Ta 和 TaN 等,可通过 原 子 层 沉 积 法 或 化 学 镀 方 法 实 现 材 料 沉积。原子层沉积技术是利用反应气体与基板之间的气-固相反应在原子级别逐层实现薄膜生长,能够精确地控制膜层厚度和组分,因此,采用该技术沉积的薄膜具有均匀性好、保形性高、纯度高等优势。但是,与化学镀工艺相比,原子层沉积成本高昂且更加耗时。化学镀是一种无需通电,利用强还原剂在含有金属离子的溶液中,将金属离子还原成金属而沉积在各种材料表面形成致密镀层的方法。通过化学镀将 Ni 沉积在通孔中形成阻隔层能阻挡 Cu 的扩散,且阻挡效果优于 TiN 和 TaN , 并 且能 够 实 现 100% 的 覆 盖率。其缺点也十分明显,由于在镀液中金属离子与还原剂同时存在,镀液的稳定性较差,并且化学镀速度较慢,排放的污染物也较难处理。溅射工艺的原理是用带电粒子轰击靶材,加速的离子轰击固体表面时,发生表面原子碰撞并发生能量和动量的转移,使靶材原子从表面逸出并淀积在基板材料上的过程,可用于在绝缘层上形成 Ti/Cu 或 Ti/Au 薄金属层。ROH 等使用高密度等离子体化学气相沉积(High density plasma chemical vapor deposition, HDPCVD)技术形成厚度为 1 μm 的 SiO2 绝缘层,并通过溅射工艺形成Ti 阻隔层和 Cu 种子层。类似的, KEE 等在Cu-SiC 复合填充的 TSV 中以 SiO2、 Ti、和 Cu 为材料分别形成 1 μm 厚的绝缘层、 0.3 μm 厚的阻隔层和 0.5 μm 厚的种子层。但是, 在溅射过程中,由于金属原子的不规则线性运动,金属原子会更大概率沉积在通孔的入口处,导致入口处较厚,而底部较薄。深宽比越高的 TSV,其内部形成统一的阻隔层和种子层的难度越大。针对此问题,MATSUDAIRA 等通过在铅纳米颗粒催化剂的作用下,用化学镀形成 CoWB 和 CoB 阻隔层,实验结果表明 W 含量提高 15%的 CoWB 薄膜在350 ℃的退火温度下具有良好的扩散阻挡作用,并且避免了孔口沉积。表 2 总结了侧壁涂层工艺的相关研究进展。沉积绝缘层的主要工艺有热氧化工艺、 PECVD 和HDPCVD。热氧化工艺因其温度较高而对衬底耐热性有较高要求;PECVD 的台阶覆盖率通过优化工艺参数可以得到改善;HDPCVD 可形成较薄的绝缘层,但成本较高。沉积阻隔层的主要工艺有原子层沉积法、化学镀和溅射。原子层沉积适用于超深TSV,且阻挡扩散效果显著;通过化学镀可实现高深宽比通孔的 100%沉积覆盖;通过溅射可实现超薄的沉积厚度。

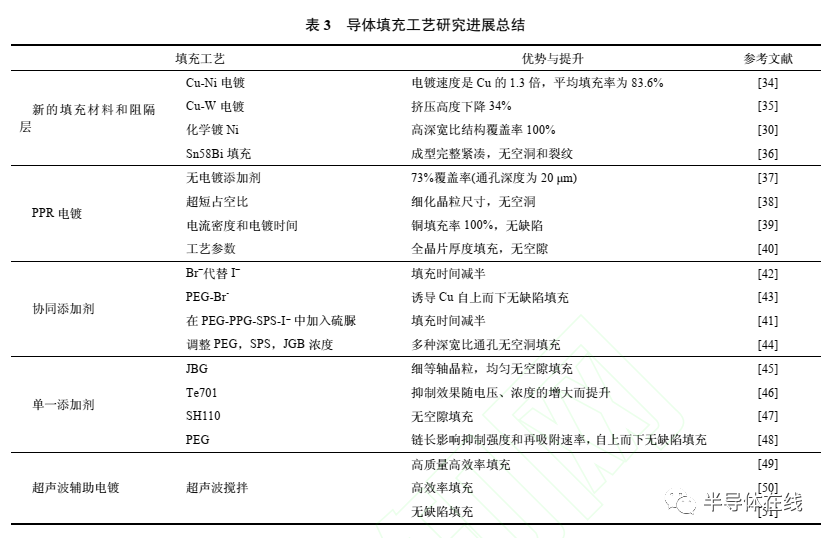

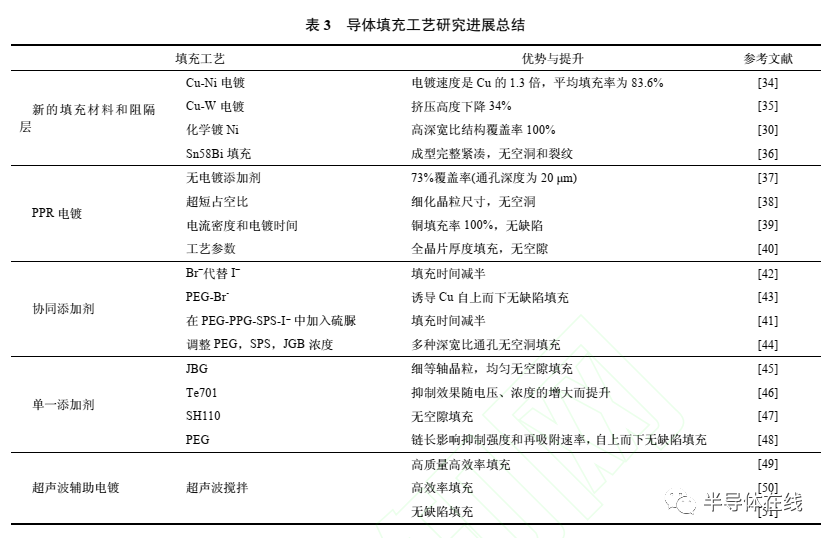

在大规模生产中, 电镀是最主要的 TSV 填充方法。研究人员致力于研究高速、高深宽比、无空洞、无缺陷的 TSV 填充方法, 而最大的挑战是电镀角效应会导致空洞的形成。为了应对这一挑战,研究人员尝试了一些新的电镀方法,如新的填充材料、周期性反向脉冲(Periodic pulse reversal, PPR)电镀、镀液添加剂和超声波辅助等。在 新 的 填 充 材 料 和 阻 隔 层 材 料 上 , HONG等通过实验发现,在同等条件下 PPR 电 镀Cu-Ni 合金的速度是 Cu 的 1.3 倍,电镀 60 min时的平均填充率为 83.6%。由于新相的成核通常发生在晶界处,并且在晶界处更容易生长,而Cu-Ni 合金镀层的晶界数量多于 Cu,因此其成核的可能性更大,填充速率更高。ROH 等通过实验发现 Cu-W 填充 TSV 的挤压高度比 Cu 填充TSV 约低 34%,这是因为 W 的存在抑制了 Cu 在高温下的扩散,从而缓解了 TSV 的挤压现象。WANG 等以 Sn58Bi 作为 TSV 的填充材料,通孔成型完整且紧凑,没有产生空洞和裂纹。由于Sn58Bi 具有典型的交替层共晶结构, 因此 Sn58Bi的润湿性和热疲劳性能十分优异。综上所述,相较于传统的 Cu 材料,新型填充材料在填充速率、挤压高度、通孔成型等方面具有显著优势。在 PPR 电镀方面, 相关研究表明 PPR 电镀能细化晶粒尺寸,获得无空洞的通孔填充,通过优化电镀参数,得到了直径为 62.5 μm、厚度为625 μm 的 TSV。PPR 电镀提高了阴极的电化学极化,降低了阴极的浓差极化,使得金属离子在阴极的沉积速率大于晶体生长速率,其结果是晶核数目增加,晶粒尺寸减小。PPR 电镀的缺点是电镀阶段为还原电流,刻蚀阶段为氧化电流,因此填充时间较长。针对此问题,研究人员发现通过改变电镀液中的抑制剂、加速剂和整平剂可以缩短填充时间。在添加剂的协同使用上, KIM 等发现在抑制剂 PEG-PPG-SPS-I-中加入硫脲能够使填充时间减半。硫脲中的-NH2 与 PEG 中的氧原子易形成氢键,进而形成硫脲与 PEG 的络合物, 并增强了络合物的稳定性;另外,硫脲中的 S 会化学吸附至 Cu 的表面,形成对电镀的显著抑制层,增强 PEG-PPG 的吸附能力和对 TSV 侧壁电镀的抑制能力, 提高了电镀效率。但是,当抑制层存在不稳定的 CuI 时,电镀效率会降低。将 PEG-PPG-SPS-I-中的 I-替换为Br-后,可以进一步缩短填充时间。由聚合物抑制剂 PEG-PPG-Br-建立的抑制层比 CuI 抑制层更加稳定, CuI 抑制层在 TSV 填充过程中会不断分离和再生,消耗了额外的电子,降低了填充效率,而 Br-基抑制层不受对流影响,能实现较高的填充效率。同时, Br-可以诱导 Cu 自下而上完成无缺 陷 的 填 充 。Br-形成 了 具 有 负 击 穿 电 位 的PEG-Br-抑制层并建立被动-主动区域,其击穿电位取决于其浓度,在适当的电位下通过选择性地激活 TSV 底部的电镀来实现 Cu 自下而上的无缺陷填充。不同添加剂对 Cu 的沉积过程呈现不同作用机制,一种添加剂可能产生多种作用,多种添加剂可能产生协同作用。例如,聚乙二醇(PEG)作为抑制剂, SPS 作为加速剂,健那绿(JBG)作为整平剂,成功地将 Cu 无空洞地填充到不同深宽比的通孔中。可以看出,在多种镀液添加剂的共同作用下,能有效抑制孔口沉积速率,提高底部沉积速率,实现通孔的无空隙均匀填充。添加剂机理研究复杂,部分添加剂的作用机理至今仍无统一定论,有待进一步明确。另外,多种添加剂的组成成分和使用比例不容易精确控制,研究人员在单一添加剂方面也做了许多尝试。在单一添加剂的使用上, TANG 等通过使用单一添加剂 JBG 形成了细小等轴晶粒填充物,完成 TSV 的均匀无空隙填充。细小等轴晶粒的形成与沉积过程中 JGB 的抑制效应有关。JGB 是季铵盐,带正电荷,因此其易吸附在阴极上并阻止铜离子反应;另一方面, JGB 分子中的 N=N 官能团也被认为可能是 JGB 吸附在 Cu 表面的反应位点, JGB 会在阴极表面分解还原, 其中 N=N 断键与铜离子还原形成竞争反应,进而减少铜离子的还原数量,抑制 Cu沉积。 DONG 等以 Te701 作为单一抑制剂,发现在高电位时抑制效果随浓度的提高而提高。在低浓度 Te701 溶液中,由于嵌段的亲水性不同,会形成不均匀的抑制层。当浓度增加时,亲水性的聚环氧乙烷嵌段会延伸到溶液中,露出空位以吸附更多的Te701 并形成致密的抑制层。WANG 等发现SH110 同时具有加速和抑制作用,且加速作用优于SPS,能够实现无空洞填充。SH110 通过 4,5-二氢噻唑(4,5‑ dihydrothiazole, DHT)和 3-巯基丙烷磺酸盐(3‑ mercaptopropane sulfonate, MPS)部分吸附在铜表面,而 SPS 仅通过 MPS 部分进行吸附。铜表面的 S-S 和 -SO3- 基团的吸附平衡使 SH110 具有加速作用, DHT 基团使 SH110 具有抑制作用。SUNG 等合成了一种 PEG 基有机添加剂,对Cu 沉积有较强的抑制作用, 通过实验发现链长会影响抑制强度和再吸附速率。综上所述,仅通过单一添加剂也可以实现自上而下、无空隙的填充效果,并且降低了工艺复杂度。在超声波辅助电镀上, XIAO 等通过实验发现超声波辅助电镀能提高 TSV 的填充质量和速度。在超声波辅助电镀中有两种力量加速了传质过程,其中一种力量是声流。当具有足够能量强度的超声波的能量被电解液吸收时,会使电解液产生显著的流动,即声能转换为电解液的动能。另一种力量是空化效应:溶液中充满蒸汽的空腔在超声波作用下成核、膨胀和塌缩。这些气泡在电解液中的剧烈塌缩会产生冲击波,从而促进质量传输。总之,传质过程的增强使铜离子可以被及时输送到 TSV 的底部,减少了电极的浓度极化,有助于提高填充质量。ZENG 等发现在超声波搅拌下,电镀填充率显著提高,超声波辅助直流电镀的最佳电流密度为 0.4ASD,是无超声波辅助直流电镀的 2 倍。CHEN等在不添加加速剂或抑制剂的条件下,使用超声波辅助化学溶液实现了高深宽比通孔的无缝、无空腔和无过载快速填充。综上所述,通过超声波辅助电镀能够解决传统电镀工艺中电流密度低、液相传质慢等问题,显著提高了填充质量和速度。然而,超声波功率并非越大越好,超声波功率过大会增强烧蚀效应, 显著降低 Cu 与 TSV 侧壁之间的粘附性,使大部分 Cu 从 TSV 侧壁脱落,导致较差的填充质量。表 3 总结了 TSV 导体填充工艺的相关研究进展。研究表明,相对于传统的 Cu 材料,新型填充材料在电镀速率、挤压高度和填充质量上均有较大优势;PPR 电镀能细化晶粒尺寸,获得无空洞的通孔填充;通过多种添加剂的协同使用可以实现自上而下、适合于多种深宽比的无缺陷填充,但多种添加剂的组成成分和使用比例不容易精确控制,通过单一添加剂也可实现自上而下的无缺陷填充;通过超声波辅助电镀可以加快电镀速度, 提高填充质量。

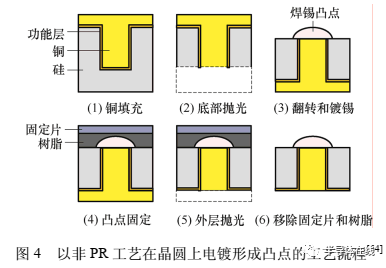

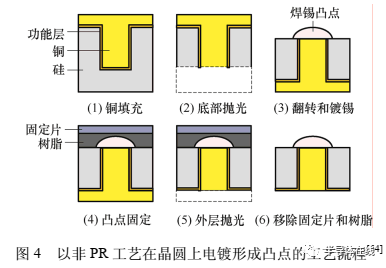

综上所述,实现无缺陷填充的关键是调整孔口和通孔底部的填充速率比,避免孔口在未完成填充时提前闭合。TSV 在制作完成后,为了实现与上下层芯片或衬底的信号连接,需要将 TSV 与 TSV、芯片和衬底相互键合,键合方式分为凸点键合和无凸点键合。制造凸点的主要工艺有焊锡凸点电镀、焊膏压印、铜柱凸点电镀和焊锡注模。混合键合可以替代凸点,实现 TSV 中 Cu-Cu 的无凸点键合。随着制造微小凸点技术的成熟,电镀正成为一种流行的凸点制造方法。通过将晶圆放入镀槽中进行电镀,实现凸点制备。但是以电镀法制备凸点的工序相对复杂,改变焊料合金的成分相对较难,需要对镀液中各组成成分的含量进行控制,且镀液的稳定性较差。凸点的尺寸对实现芯片的理想堆叠非常重要。在 电 镀 过 程 中 , 通 常 在 硅 片 上 使 用 光 刻 胶(Photoresist, PR)来精确地控制凸点尺寸。通过使用PR 模具可以得到小尺寸的细间距铜柱凸点。但是,高精度 PR 模具的制造过程复杂且成本较高。对此, CHO 等以非光刻工艺电镀出 Sn-3.5Ag 焊料凸点。晶圆背面需要研磨至 Cu 填充物暴露在表面且无挤出,随后电流流经通孔至凸点表面,在没有PR 模具的情况下直接在 Cu 填充物上镀 Sn。在镀Sn 过程中,凸点的高度和宽度随着电镀时间和电流密度的增加而增加,稳定的电流有助于在非 PR 模具工艺中形成形状相同、大小均匀的凸点。图 4 展示了在不使用 PR 模具的条件下以直流电镀在铜塞上形成凸点的工艺步骤。对于非 PR 模具工艺,TSV 中的焊缝、空洞和不完全填充等缺陷会导致不规则凸点的形成。因此, TSV 的填充质量会直接影响到焊锡凸点的制备。

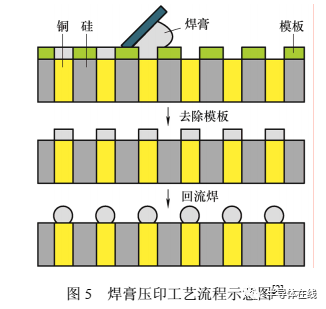

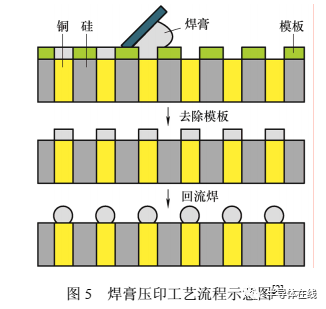

焊膏压印工艺是通过在 TSV 上的细间距模板压印焊膏,然后回流焊,最终形成焊锡凸点,其工艺过程如图 5 所示。在焊膏压印中,为了形成无缺陷的凸点,需要特别注意基板表面状况、基板-模板比(模板开口尺寸,间距大小,模板厚度),压印速度和压力大小等各种参数。焊膏压印具有简化生产工艺和降低成本的优势, KUMAR 等通过焊膏压印工艺,以 SAC305 为焊膏形成了晶圆级凸点。但由于模板的工艺限制,通常不采用焊膏压印来制造超细间距的 TSV 基板。针对此问题,研究人员发现用于制造超细间距模具的激光边缘技术和 SAC305焊膏可以简化焊膏压印过程。

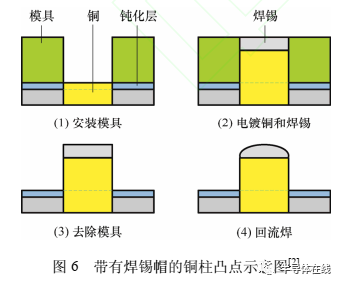

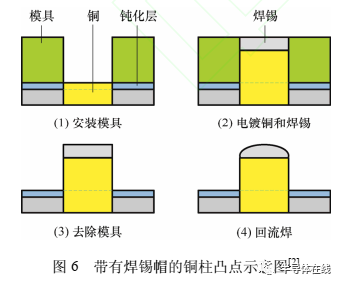

铜柱凸点(Copper pillar bump, CPB)可替代传统焊料凸点, 其结构和生产工艺与电镀焊料凸点类似,制造过程主要结合了光刻和电镀工艺。CPB 的制造过程如图 6 所示。CPB 工艺是通过电镀在 TSV 上形成一个较高的铜柱凸点,并在凸点的顶部镀上一层较薄的焊锡膜。与传统焊料凸点相比较, CPB 结构使得凸点中焊料的体积分数显著减小,而铜柱主要承担了大部分的支撑高度。

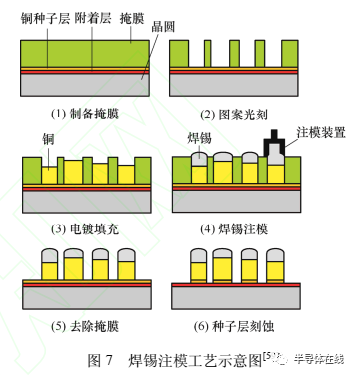

通过电镀法在 TSV 上形成焊锡凸点时, 凸点间距通常在 70~140 μm 之间。但是, 当间距小于 70 μm时,在回流焊的过程中相邻焊点可能会发生桥接。通过 CPB 工艺可以形成更小间距的凸点而不产生桥接,并且具有良好的散热性能和较高的机械屈服强度。在热处理过程中,由于金属原子的扩散,焊锡膜与铜柱的界面处会形成金属间化合物,严重影响互连可靠性。通过在铜柱和锡层之间添加镍层能有效缓解金属间化合物的生成,提高凸点互连可靠性。焊锡注模(Injection molded solder, IMS)工艺又称铜柱上的焊锡注入,在这个过程中,熔化的焊锡金属从喷嘴尖端被挤出到铜柱上。IMS 的过程如图7 所示。IMS 工艺包含以下步骤:在晶圆上形成种子层和 PR 样板、铜柱电镀、焊锡注入、 PR 和种子层剥离。

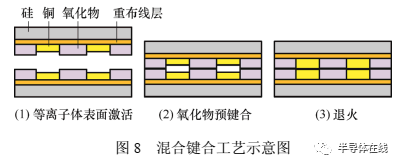

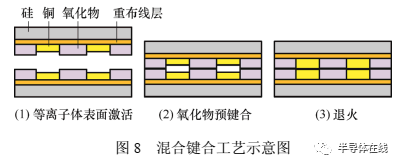

IMS 工艺具有很多优点:便于提供三元体系无铅焊料, 如 Sn-Ag-Cu, 并且 IMS 工艺可由共晶 PnSn焊料拓展到无铅焊料;与电镀相比,凸点的尺寸不受晶圆位置的影响,对于不同高度、不同尺寸的铜柱,通过 IMS 工艺最终可以形成等高的凸点;IMS 是无助焊剂工艺,可以形成各种尺寸的焊点。缺点是其需要耐高温 PR 材料, 在焊料固化前 PR 要充 当 熔 化焊 料 贮 存器 的 屏 障 。针 对 此问 题 ,MUKAWA 等介绍了 IMS 工艺中具有高热稳定性的 PR, 并由实验制得直径为 20 μm、 间距小于 40 μm的凸点。获得高焊料填充率的重要因素之一是减少PR 在高温下的气体排出量, 气体会阻碍焊料填充到PR 模具中, 因此热去除基础聚合物中的不稳定单元有助于减少 IMS 工艺中的排气,实现稳定的焊料填充和高质量凸点制备。混合键合是一种实现介质层与介质层、金属与金属界面无缝隙键合的技术,其工艺过程如图 8 所示。在 TSV 键合中,介质层通常为SiO2,金属通常为 Cu。SiO2 介质层为集成单元提供机械支撑与电气隔离,Cu-Cu 键合提供芯片间的垂直电气互连。对于 Cu 和SiO2 混合键合结构,首先要得到具有亲水性、粗糙度小的待键合表面,然后进行直接键合,最后进行退火处理。退火在增强 SiO2-SiO2 键合强度的同时,也促进了 Cu 晶粒的生长和扩散以实现 Cu-Cu 键合。

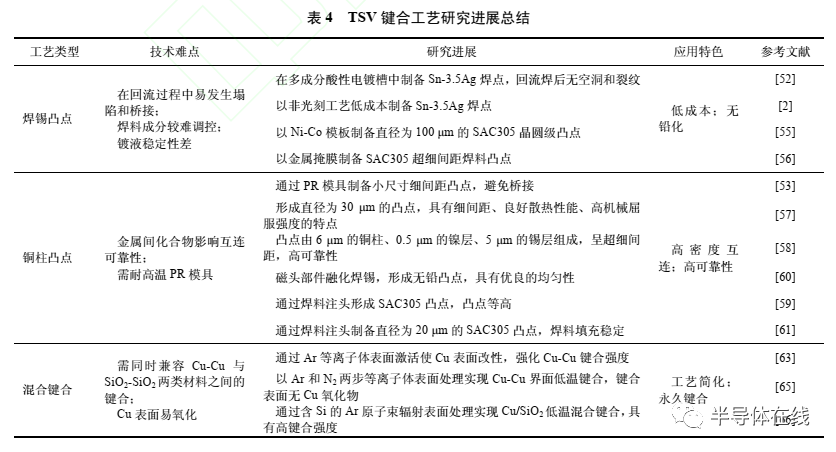

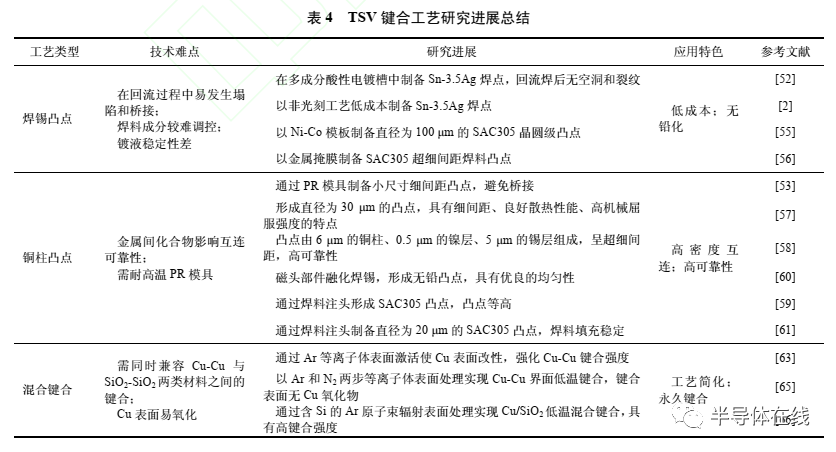

在混合键合工艺中,需要对待键合表面进行等离子或快速原子束表面激活处理。通过表面激活可以提高表面的活性、悬挂键密度和表面能,从而增大键合强度。Ar 等离子体通过离子轰击将 Cu 表面变为多孔的形态,增大了 Cu 的表面粗糙度,同时能够减少 Cu 表面的-OH 污染物, 提高 Cu 表面的润湿性。但是,在经过 Ar 等离子体处理的 Cu 表面上会形成 Cu2O,严重影响电气连接性能。对此NAKAHIRO 等通过实验发现,在 Ar 等离子体中加入适量的 H2 等离子体可有效抑制 Cu2O 和 CuO的生成, 但是 H2 等离子体处理需要在高温条件下进行,且易引发安全问题。针对该问题, SEO 等采用 Ar 和 N2 两步等离子体表面处理,能有效去除金属氧化物且无需高温条件。N2 等离子体表面处理会形成 Cu4N 钝化层, 原子缺陷会使顶层的 Cu 表面产生电荷漂移,提高迁移率。同时, N2 等离子体处理也是激活 SiO2 介质层表面的常用方法。但是,表面激活对 SiO2 介质层键合强度的影响较弱,目前有研究关注 Cu 和 SiO2两种材料的整体混合键合过程。通过使用含 Si 的 Ar 原子束辐射处理 Cu 和 SiO2 表面,然后进行亲水性键合,实现在室温下的混合键合,且键合强度显著提升。通过混合键合和无凸点互连技术能够实现芯片的超高密度垂直互连,促进芯片向高性能、微型化和低功耗方向发展。以台积电的无凸点 3D 集成SoIC 技术为例, SoIC 可与 CoWoS、集成扇出型封装等技术实现深度异质集成整合,将原本需要在单个 SoC 芯片上实现的功能分解成多个 Chiplet 来实现,再通过集成 SoIC 实现灵活整合,其芯片具有设计成本低、速度快、宽带宽和低功耗的优势。然而,当前该技术在设计规则、平整度、清洁度、材料选择等方面仍面临许多挑战。表 4 总结了 TSV 键合工艺的相关研究进展。通过电镀形成的焊锡凸点在回流焊后无裂缝产生,大小均匀。焊膏压印工艺的关键在于基板参数、压印速度和压力大小, 能够形成晶圆级细间距焊锡凸点。相比于焊锡凸点,电镀铜柱凸点具有良好的散热性和高可靠性,并且不会发生桥接。焊锡注模工艺最大优点是能形成均匀、等高的凸点,弥补了因通孔内填充物高度不一致导致凸点高度不一致的问题。与凸点键合相比,混合键合简化了工艺步骤和键合结构, Cu 密封在无机介质层中,不需要凸点下金属层和底部填充物,提高了散热性能、电气性能、热机械可靠性和封装密度。

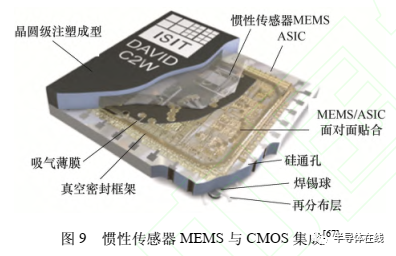

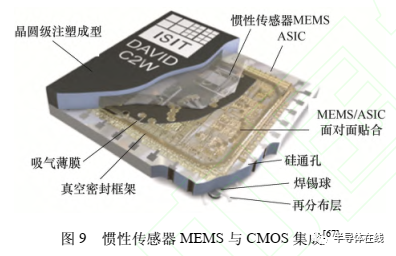

在用于单个 MEMS 的低密度 TSV 应用中, TSV的基本功能是将 MEMS 的电信号从晶圆的正面传导到背面。同时, MEMS 芯片可以堆叠在 CMOS芯片上,实现 MEMS 与 CMOS 芯片的三维集成。如图 9 所示的互联结构分别将 MEMS 和 CMOS 芯片作为盖子和基板进行面对面贴合,是一种 MEMS真空封装和 CMOS 集成的典型例子。首先要在读出集成电路(Read-out integrated circuit, ROIC)上制作TSV, 将信号连接到 ROIC 背面, 然后通过 Au-Sn键合, 将 MEMS 或传感器面对面地键合到 ROIC 上。为了达到可接受的通孔间距, TSV 直径要求在50 µm 到 100 µm 之间,因此选择 DRIE 工艺以获得具有严格垂直侧壁的通孔轮廓。通过 MOCVD 工艺在厚度为 50 nm 的 TiN 阻隔层上沉积厚度约为200 nm 的 Cu 以完成侧壁金属化,随后用弹性、低CTE 材料填充通孔。

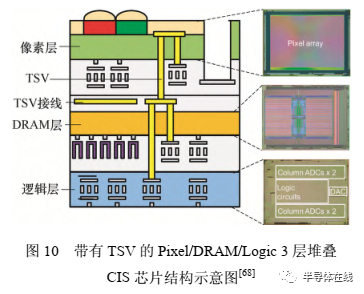

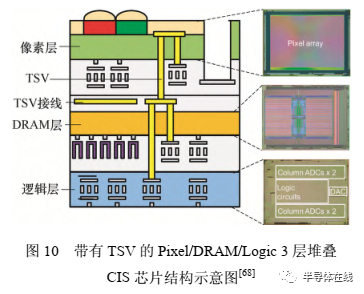

在用于传感器/MEMS 阵列和 CMOS 集成的高密度 TSV 应用中,高密度 TSV 为传感器阵列提供了较高的带宽。典型应用之一是 CMOS 图像传感器(CMOS image sensor, CIS)。索尼 IMX400 采用了一种三层集成的 CIS。从上到下依次是像素层、DRAM 层和逻辑层,芯片的整体厚度为 130 μm。图 10 展示了 Pixel/DRAM/Logic 三层堆叠 CIS 芯片的结构。通过两层 TSV 和重布线层实现了三层互联,连接像素层和 DRAM 层的 TSV 有 1.5 万个,连接 DRAM 层和逻辑层的 TSV 有 2 万个。其中,TSV 的最小直径为 2.5 μm,最小间距为 6.3 μm,重布线层的线宽为 2 μm,最小间距为 0.64 μm。在应力迁移测试中,模块在 175℃的温度下退火 1 000 h后, TSV 的电阻偏移被控制在 2%以内。

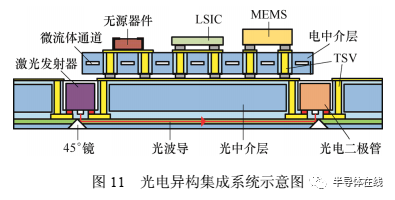

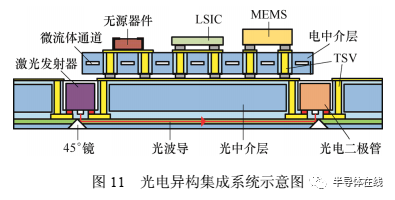

3D 集成虽然具有集成密度高、占用面积小、短互连和高带宽等优点,但是在技术可行性和成本上具有一定局限性。对比 3D 集成,一种更经济、更简单的集成技术是 TSV 中介层技术, 即 2.5D 集成。中介层是芯片与封装基板之间的中间衬底,用于多芯片集成和 I/O 再分配。中介层的典型应用之一是光电异构集成系统,该系统集成了大规模集成电路(Large scale integration circuit, LSIC)、 MEMS 和光子器件,如图 11 所示。LSIC、无源器件和传感器等芯片被安装在电中介层上,激光发射器和光电二极管等光子器件被嵌入到光中介层中, 通过 TSV 连接每个中介层的两面,实现光子器件与电子器件的信号互联。在制备中介层中的 TSV 时,通过使用DRIE 工艺在衬底上形成直径为 40 µm、深度为150 µm 的通孔,之后在 900 ℃的温度下以热氧化法制备 1 µm 厚的 SiO2 绝缘层,以溅射工艺在 TSV侧壁上沉积 0.3 µm 厚的 Ta 阻隔层和 0.5 µm 厚的Cu 种子层, 随后电镀 Cu 完成 TSV 填充, 并在 TSV上制备了厚度为 7 µm 的 Cu-Sn 微凸点。

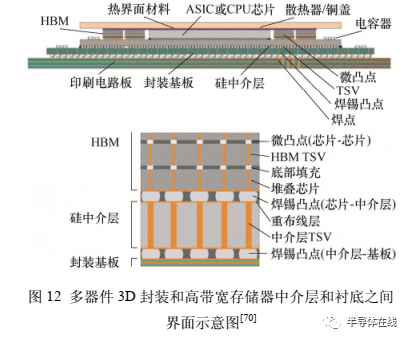

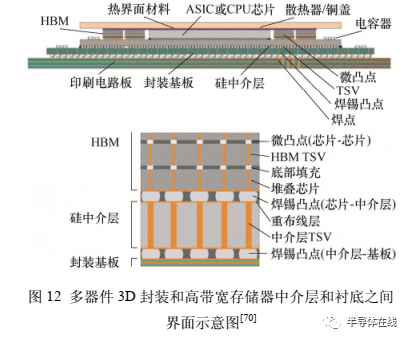

高速信号传输和大容量存储的需求要求电子器件向更大的尺寸和更复杂的多芯片堆叠结构发展。如图 12 所示的多层结构具有不同类型和不同规模的互连结构,在 HBM 之间、 HBM 与基板之间都连有微凸点和 TSV。由于多层结构的初始状态并非绝对均匀,所以连接点的微观结构会不断演化,进而影响整体结构的性能。

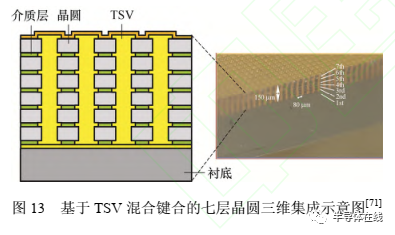

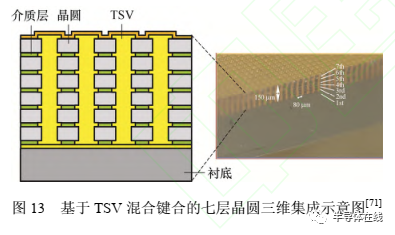

TSV 不仅可以连接芯片和基板,也可用于晶圆之间的无凸点互连。OHBA 等通过使用晶圆混合键合技术,将七层薄形化晶圆(单层晶圆厚度为20 μm)进行堆叠, 并使用直径为 30 μm 的 TSV 将各层连接,如图 13 所示。在制备 TSV 的过程中,通过 Bosch 刻蚀工艺形成直径为 30 μm 的通孔,以PECVD 技术沉积氮化硅绝缘层,以溅射工艺沉积Ti/TiN 阻隔层,最后电镀 Cu 完成通孔填充。由于晶圆混合键合工艺不需要金属凸点连接,所以晶圆之间的间隙仅有 5 μm,组成的多晶圆模块(含衬底晶圆)的总厚度小于 1 mm。

TSV 的技术路线大致有两种方向,一是在外围焊盘上构造 TSV 的三维集成结构, TSV 的设计可以放宽到焊盘间距,不仅能改善性能,还可以在不修改原始芯片布局的情况下提高形状系数;二是先进三维集成,堆叠芯片中的电路模块需要直接与 TSV和微凸点连接,为避免浪费芯片的空余空间,其间距要缩小到 5 μm 以下。TSV 技术在 3D-SiP 中是必要的互连技术之一,是倒装芯片和引线键合技术较好的替代或补充方案。对比传统封装, TSV 实现了芯片间、器件间在Z 轴方向上的延拓和连接, 使 3D 空间堆叠的密度达到最大,同时保持较小的尺寸,显著提高了信号的传输速度,降低了芯片的功耗。业内人士将 TSV 视作继引线键合和倒装芯片之后的第三代封装技术。当前, TSV 技术面临着许多挑战,如超薄晶圆的生产难度大, TSV 的制造成本高昂;由于 Si 和Cu 的热膨胀系数存在较大差异,在制造 TSV 的过程中会产生较大的应力;系统结构的密度进一步提高,层间间距进一步缩小,高密度 TSV 结构会导致热量的集中;垂直互联结构包含了更多的节点和互连线, 当信号经过 TSV 时可能会产生延迟、损耗和串扰,在射频芯片封装中, TSV 对射频信号的传输能力尤为关键;TSV 互联结构对材料的兼容性、装配精度和堆叠芯片尺寸有着更严苛的要求。为了解决 TSV 所面临的问题, 研究人员正在从设计、制造和应用等方向上进行探索和尝试。从材料的角度, 通过探索新材料和新工艺抑制衬底损耗、降低应力和实现良好的阻抗匹配。从结构的角度,同轴空气间隙 TSV 等新结构能够降低整体的寄生电容和能量损耗;通过优化结构布局可以减少 TSV的使用数量和成本。从填充的角度,不同于传统的 Cu、 W 和多晶硅等填充物,通过在通孔中填充单壁碳纳米管,可以明显改善 TSV 的电学、热学和机械特性。;另外,田苗等提出了一种通孔双面分步填充的工艺,避免了自底向上的高难度填充工艺,大大降低了 TSV 的制造难度和成本。从键合的角度,以混合键合为主的无凸点键合技术正成为凸点键合的替代方案之一,该技术将互连层的高度从微米级降至纳米级,进一步提升了互连密度和热机械可靠性。但其生产成本仍然非常昂贵,未来将在更有效的激活方式、更创新的结构设计等方面进行突破以降低键合成本。高密度集成结构要求 TSV 具有更小尺寸、 更细间距和更高深宽比, 高可靠性器件要求 TSV 在高速率电镀下仍能实现完美填充。在未来,随着材料科学和机械技术的不断进步, TSV 技术将实现更加完美的 3D-SiP。3D-SiP 作为目前先进封装技术之一拥有很开阔的发展前景,与传统封装相比,其最大的进步在垂直方向上实现了芯片、器件、基板和晶圆等分层的互联,使封装效率显著提升。本文聚焦于后摩尔时代的热门先进封装技术——3D-SiP,重点介绍了实现垂直互联结构的关键技术:硅通孔技术,从技术背景、生产制造、键合工艺、 实际应用等方面的研究现状进行了总结和归纳,探讨了该技术当前面临的挑战和未来的发展趋势,为后续 TSV 技术的发展提供参考和借鉴。

来源:机械工程学报,作者王美玉,张浩波,胡伟波,梅云辉注:文内信息仅为提供分享交流渠道,不代表本公众号观点作者:王美玉 1 张浩波 1 胡伟波 1 梅云辉 2(1. 南开大学电子信息与光学工程学院 天津 300350;

2. 天津工业大学电气工程学院 天津 300387)