|

封装摩尔定律将取代ICs摩尔定律时间:2019-11-27 在过去的六十年,摩尔定律(Moore’s

Law)是晶体管尺寸缩小、晶体管集成和降低成本的驱动力。但是电子系统,比如智能手机、无人驾驶汽车、类人机器人,则不仅仅包含晶体管和ICs。ICs摩尔定律(Moore’s

Law for

ICs)将电子信息产业引导成长为万亿美元产业,但是ICs摩尔定律(包括约每两年就增加晶体管集成度、降低成本)由于量子隧穿效应等因素,即将到达物理极限。因此,美国佐治亚理工学院(Georgia

Tech)的Rao R. Tummala教授认为,封装摩尔定律(Moore’s Law for

Packaging)在短期内,至少于降低成本方面,将会替代ICs摩尔定律(Moore’s Law for

ICs)。降低晶体管尺寸(即晶体管缩放比例)以及它们的互连和集成度是ICs摩尔定律的基础;而有源、无源系统元件的尺寸减小,及其互连和集成度增加,亦可成为封装摩尔定律的基石。

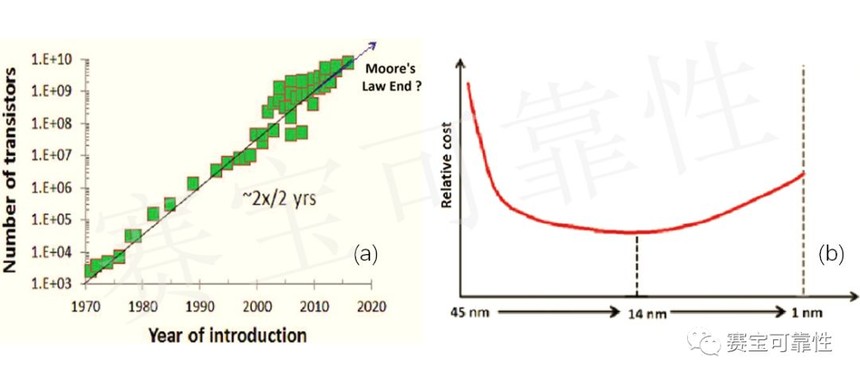

ICs摩尔定律预测了每18-24个月晶体管数量增加一倍(图1a),与此同时成本也随之降低。因此,Prof. Tummala提出封装摩尔定律趋势也类似。其中,互连由计算系统(逻辑和存储器)驱动。模拟人脑的人工智能时代的到来,也是封装摩尔定律的另一驱动力。

目前,封装摩尔定律最先进的是基于晶圆的硅封装(Silicon Packaging)。但是硅基封装有着诸多限制,如材料、基体、互连及系统。在材料层面,Si基封装的电损耗和介电常数很高。在互连层面,Si基封装的电容和电阻很大,导致RC延迟较大。此外,Si基封装的在成本层面上与摩尔定律不兼容,而成本对于ICs摩尔定律而言是定律延续的基础。在系统层面,与ICs完美兼容的Si中介层(Si-Interposer)与基板(Boards)完全不兼容,需要额外的封装,因此使得系统级互连长度增加。

图1 (a)ICs摩尔定律 (b)晶体管栅长与制造成本的关系

ICs摩尔定律

在过去60年,ICs摩尔定律被事实证明是精准的,且被作为半导体产业的R&D目标。但是,在晶体管尺寸减小方面,由于量子效应,当减小至分子级尺寸时,电子隧穿效应会导致短路。这是ICs摩尔定律的极限,被称之为“摩尔定律终结的开始”(下一个10年内即将发生)。在成本方面,摩尔第二定律指出,在给定尺寸的晶片上,随着节点到节点之间每单位面积晶体管的数量的增长,每个晶体管的制造成本会下降。而半导体产业已得出结论是,当晶体管栅长低于14nm时,单个晶体管的制造成本鲜有降低,反而随着栅长继续减小而有所增长(图1b)。

封装摩尔定律:互连密度 or I/Os密度?

封装摩尔定律的概念(图2a)可以从1960年代后期出现的双列直插式(DIP)封装形式开始解释:DIP的I/Os数<16,随后出现的外围四方扁平封装(QFP)的I/Os数达到64-304,而后在1980和1990年代,陶瓷封装的I/Os数已经分别达到了121和1000。但是这个时期的陶瓷封装有诸多限制,如厚膜粘贴技术中100μm的线宽和过孔,限制了I/Os数的继续增加。此外,陶瓷的高介电常数和低电导率(共烧金属如W,Mo或Ag-Pd)也限制了陶瓷封装的性能,虽然后期出现的LTCC技术部分地解决了这些局限性,特别是在顶部制作了类似于重布线层(Redistribution Layer,RDL)的薄膜布线。这些局限性促进了有机层压封装的发展,包括薄膜材料积层及工艺技术,可以使I/Os数超过5000。当前,大幅提高I/Os数的唯一办法是基于晶圆的硅封装,其I/Os可达到200,000个。

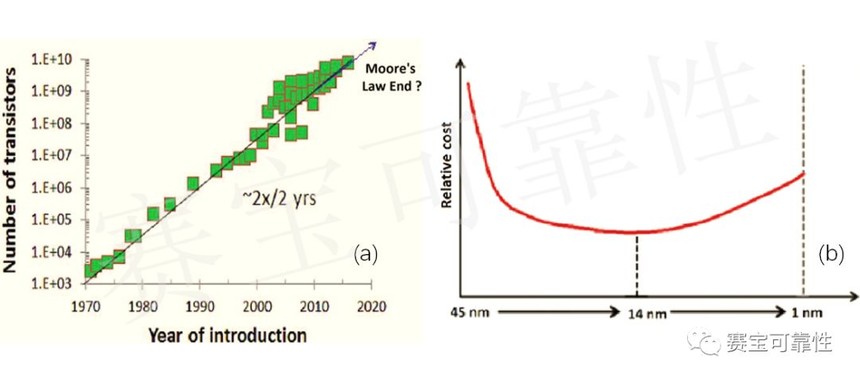

图2 (a)I/Os封装摩尔定律(b)封装类型演进伴随着单位面积成本降低

封装摩尔定律:成本

与ICs摩尔定律类似,成本对于封装摩尔定律也是一个重要因素。图2b展示了各个封装类型节点演进伴随着单位面积成本的降低趋势(1980-2020),其中唯一的例外是硅中介层,其成本是封装摩尔定律预测值的3-5倍,而佐治亚理工学院和其工业合作方共同研发的玻璃面板封装(Glass Panel Packaging)的成本是符合封装摩尔定律预测趋势的。

2010年后出现的两种封装形式:硅封装互连(Silicon Package Interconnections)及嵌入式封装互连(Embedded Package Interconnections)。

硅封装是最先进的多芯片封装,I/Os数可达200,000个,延续了IBM在1990年代的”100-chip”的多芯片陶瓷封装的概念,沿用了同样的功率分配、信号传输、芯片背面散热、倒装芯片组装技术。除此之外,还新开发了两个关键技术:硅通孔(TSV)和RDL。博世(Bosch)在高带宽存储产品中的TSV制造工艺将TSV与硅中介层的整合度提升到了相当成熟的水平。RDLs是后段制程BEOL(Back End of Line)工艺前身的重组;与有机封装或陶瓷封装相比,BEOL的制造设备是Si中介层能实现高I/Os数的重要因素。

目前,Intel在EMIB (Embedded Multi-Die Interconnect Bridge)中采用了2μm线宽的Si中介层,而AMD的HBM(High Bandwidth Memory)中的GPU(Graphics Processing Unit)则是采用了1μm线宽,Xilinx在其FPGA(Field Programmable Gate Array)应用中的线宽<0.5μm。AMD对外宣称其Radeon Fury器件的GPU裸片(尺寸596 mm2)的I/Os达到了190,000个,与Xilinx在其Virtex-7 2000T FPGA产品中的I/Os数处于相同数量级。

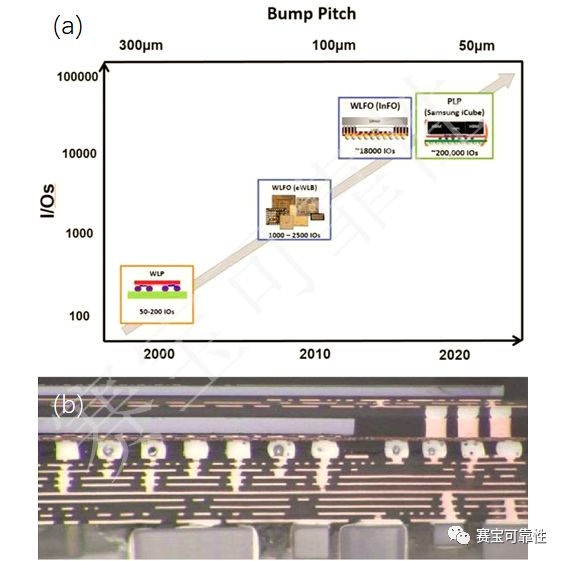

嵌入式封装意味着芯片是嵌入/埋入到封装体或板内,且嵌入的ICs之间的互连则可通过晶圆BEOL工具或封装工具来实现。图3a展示了从晶圆级(WLP)、芯片级封装(CSP)到晶圆级扇出型封装(WLFO,如eWLB、InFO)、面板级封装(PLP)技术的I/Os演变进程。英飞凌(Infineon)是第一家推出面向射频和模拟应用的晶圆扇出封装(Wafer Fan-Out,WFO)的公司,而台积电TSMC于2016年为Apple iPhone 7引入了首个大批量嵌入式晶圆扇出封装(eWFO),即集成型扇出(InFO),见图3b;当前InFO中约1cm2面积的应用处理器中凸点间距(Bump Pitch)为80μm。

图3 (a)从晶圆级封装(WLP)到面板级封装(PLP)的I/Os演化趋势 (b)台积电TSMC在iPhone 7中的eWFO封装

WFO封装的I/Os数和终端应用场合都在增长,但是也存在着一系列的技术限制,如裸片放置精度、裸片位置漂移、塑封化合物收缩、晶圆翘曲、大尺寸封装的板级可靠性、多芯片的可修复性、散热、>15mm尺寸封装的高成本等。面板扇出(Panel-Fanout)技术的开发就是为了在有机、无机层压板的层面上解决上述部分技术限制,比如佐治亚理工学院推出的玻璃面板嵌入(Glass Panel Embedding,GPE)技术及三星的iCube技术。

封装摩尔定律的未来

1、扩展Si封装互连; 2、开发大面板、低电容和低电阻的无机玻璃面板嵌入式(GPE)封装; 3、开发无需塑封化合物和组装的面板嵌入技术;

4、发展光电互连技术。 |